1. 摘要与核心贡献 摘要清晰指出,随着网络链路速度扩展至 100Gbps 乃至更高,传统 I/O 加速技术(如 Intel 的 DDIO 和 RDMA)由于 LLC 利用率低而性能受限。CEIO 的核心创新在于:在 NIC 入口处部署 I/O 管理器,通过信用-based 主动流控制将 I/O 速率限制在 LLC 容量之内,同时利用 SmartNIC 板载内存进行弹性缓冲,避免丢包和网络拥塞控制(CCA)被意外触发。作者强调,CEIO 不仅解决了现有方案(HostCC 的反应式控制和 ShRing 的固定缓冲)的慢响应与丢包问题,还通过优先保障 CPU-involved 流走快速路径(NIC→LLC→CPU/DRAM)、CPU-bypass 流走慢路径(NIC→on-NIC Memory→CPU/DRAM)的方式,实现了 LLC 零缺失下的线速吞吐和微秒级尾延迟。实验在 200Gbps 真实环境中验证了这些优势,充分证明了 CEIO 在动态流量分布和网络突发场景下的鲁棒性。

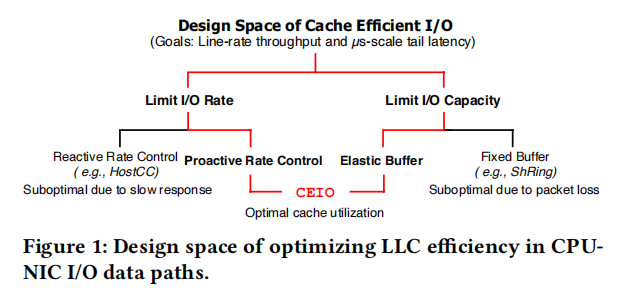

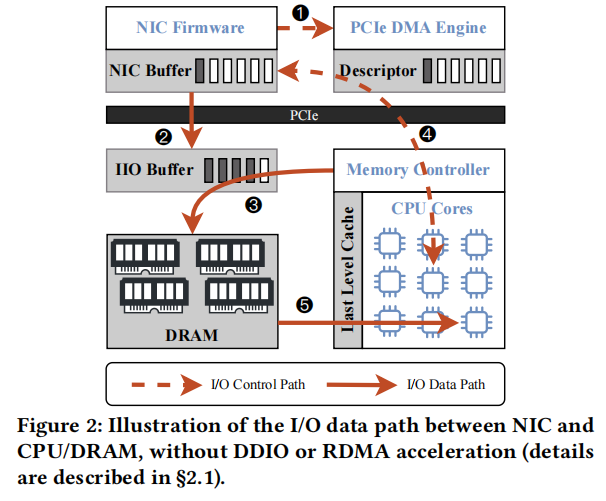

2. 引言与研究动机 引言部分详细描述了网络 I/O 系统在数据中心中的核心地位:NIC 收包后需经 DMA 写入主机内存,再由 CPU 完成协议处理和 payload 处理。随着带宽激增,CPU 成为瓶颈,DDIO(让数据直写 LLC)和 RDMA(旁路 CPU)虽能加速,但 LLC 容量有限(通常数十 MB)且被多核、多个 NIC 共享,一旦 in-flight 数据量超过 LLC 容量,就会产生大量 LLC 缺失,导致 CPU 额外从 DRAM 取数,延迟骤增至 100ns 以上,吞吐量和多核并行效率大幅下降。作者通过 200Gbps、1024B 包的例子量化说明:每个 I/O 操作必须在 41.8ns 内完成,任何 LLC 缺失都会打破线速要求。现有工作分为“限速率”(HostCC 反应式降 DMA 率)和“限容量”(ShRing 固定缓冲小于 LLC),但均因慢响应或频繁触发 CCA 而在实际动态场景下性能退化高达 1.9 倍。这直接引出 CEIO 的核心洞见:在 NIC 入口实现主动信用控制 + 弹性缓冲,从而在 LLC 溢出前就精准调控 I/O 速率,同时避免丢包。

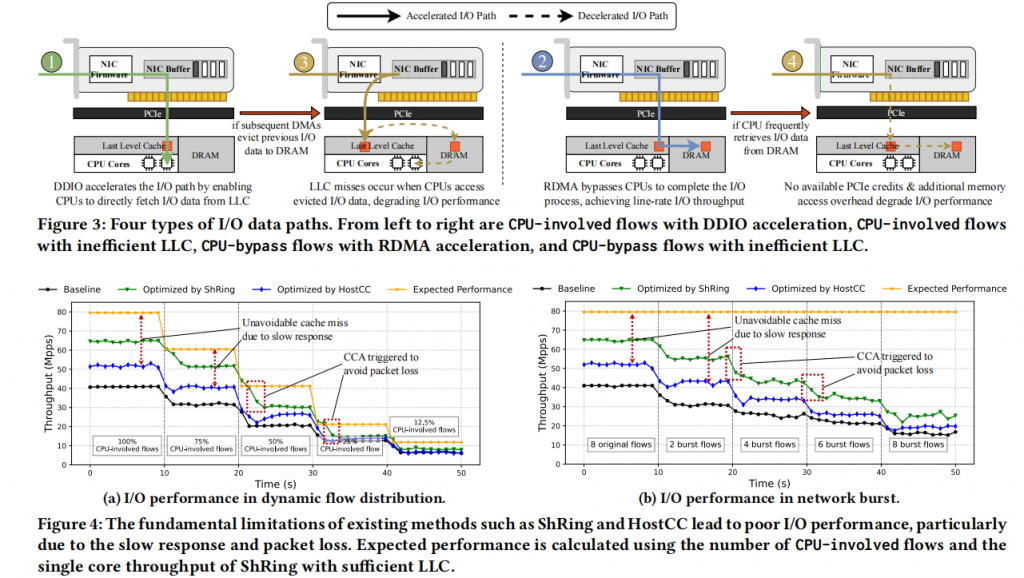

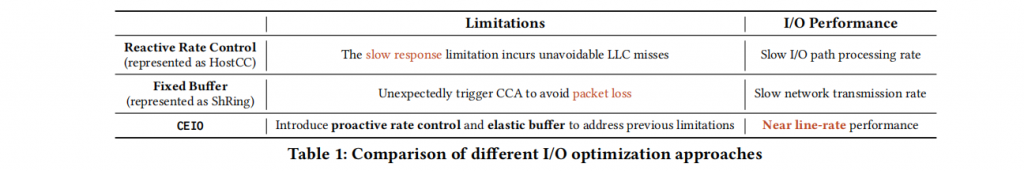

3. 背景知识与现有方案局限性 第 2 节系统梳理了网络 I/O 数据路径(图 2)、DDIO 与 RDMA 的加速原理(图 3)以及 LLC 管理的必要性。作者将 I/O 流分为 CPU-involved(DDIO 加速)和 CPU-bypass(RDMA 旁路)两类,两者均依赖 LLC,但共享导致冲突。现有方案中,HostCC 依赖 IIO 缓冲占用信号反应式降速,容易在 LLC 缺失已发生后才触发,导致慢 I/O 处理;ShRing 则固定缓冲大小以消除缺失,却频繁因缓冲满而触发 DCTCP 等 CCA,造成网络发送速率不稳定。作者在 200Gbps 双机环境下用 eRPC(CPU-involved)和 LineFS(CPU-bypass)进行动态流量切换与网络突发实验(图 4),量化证明两者性能远低于“无限 LLC”预期,最高退化 1.9 倍。表 1 对比清晰显示:CEIO 通过主动控制 + 弹性缓冲,完美规避了上述两大根本局限,为后续设计奠定基础。

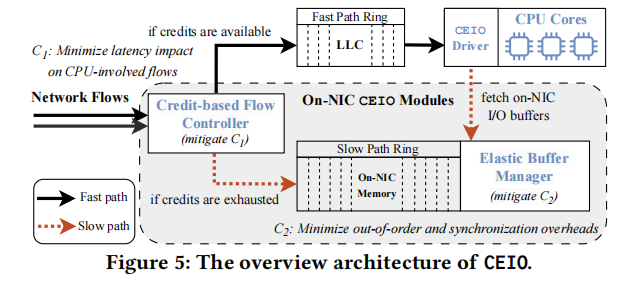

4. CEIO 架构概述 第 3 节给出 CEIO 高层设计(图 5)。核心是在 SmartNIC 上部署 I/O 管理器:(1)信用-based 流控制——所有流在 DMA 前申请信用,总信用等于 LLC 容量(公式 1),信用耗尽后自动切换至 on-NIC 缓冲;(2)弹性缓冲——超过 LLC 容量的包暂存于 SmartNIC DRAM,避免丢包和 CCA 触发。CEIO 将数据路径分为快速路径(零缺失)和慢路径(额外 PCIe 延迟),并通过两个关键挑战解决机制确保性能:一是信用分配策略优先保障 CPU-involved 流走快速路径;二是弹性缓冲管理器实现顺序保证与异步 DMA,消除重排序和同步开销。整体架构完全兼容现有 DPDK/RDMA 库,仅需替换少量 recv() 调用即可透明使用。

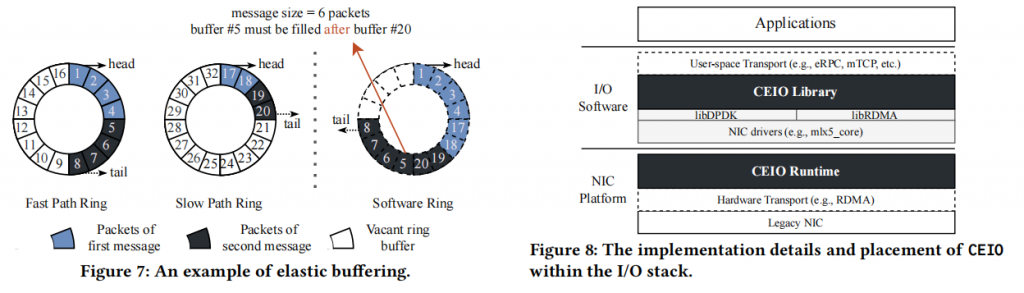

5. CEIO 详细设计 第 4 节是论文技术核心,分为两大模块。 4.1 主动信用-based 流控制:作者摒弃传统多优先级队列,转而采用“懒信用释放”机制——仅在批量消息处理完成后才归还信用。CPU-involved 流因轮询高效、处理快而快速归还信用,CPU-bypass 流(大消息)则因 RDMA Write-with-immediate 信号后才释放而快速耗尽信用,自然实现“CPU-involved 优先快速路径”。信用分配采用 Algorithm 1,在新流到达时按比例均匀重分配,并通过欠账机制(I 集合)保证公平性。同时引入“活跃流”策略 + 轮询调度,回收不活跃流信用,实现数千流规模下的高效扩展。 4.2 弹性缓冲:设计 SW Ring(软件环)统一快/慢路径硬件环,保证包序(相位互斥 + 指针交替更新);异步 DMA(async_recv() API)允许应用在处理快速路径包的同时,驱动程序后台发起慢路径 DMA,消除 CPU 阻塞。图 7 用具体例子生动展示了弹性缓冲的有序、异步工作流程。

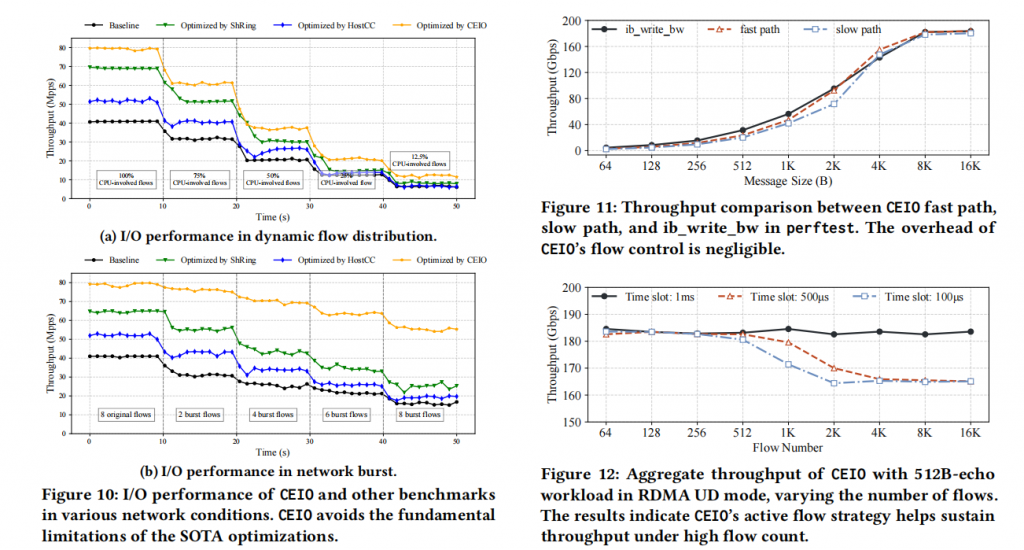

6. 实现细节 第 5 节详细说明了 CEIO 在 NVIDIA BlueField-3 DPU 上的完整实现。CEIO 库基于 DOCA SDK、DPDK 和 MLNX_OFED 构建,向上暴露 recv() / async_recv() / post_recv() 等 socket-like API,向下利用 RMT 引擎实现流表匹配与 DMA 转向,利用 ARM 核运行信用控制器和缓冲管理器。实现完全透明:上层应用(如 gRPC、eRPC、LineFS)只需替换少量 I/O 调用,无需修改传输协议或内核栈;硬件依赖仅为常见 SmartNIC 特性(RMT + 板载 DRAM),极易移植至其他厂商 NIC。作者还特别强调零拷贝支持和慢路径优化,确保兼容性与高性能兼得。

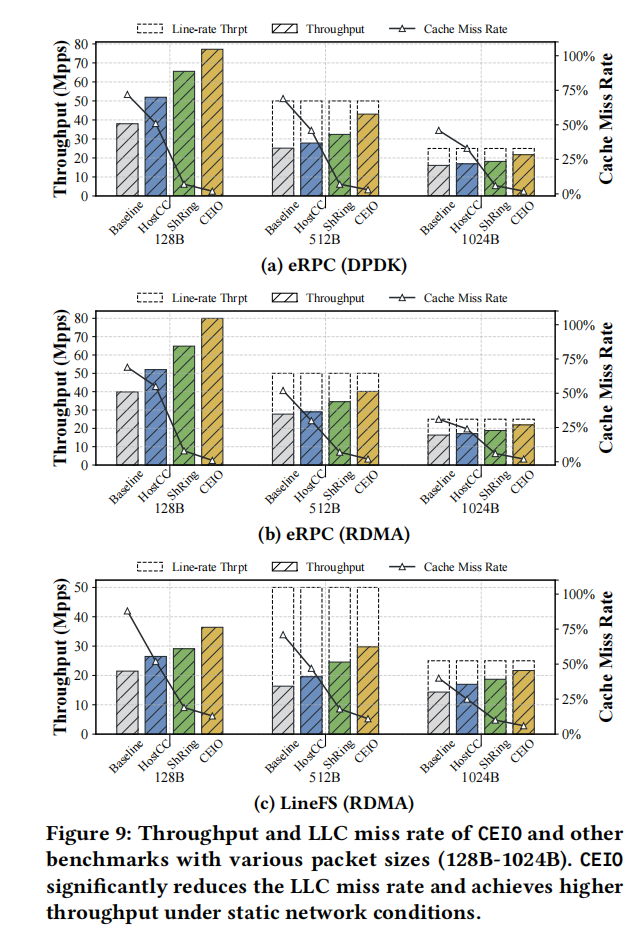

7. 实验评估 第 6 节通过真实工作负载(eRPC 键值存储 + LineFS 文件系统)在 200Gbps 环境下全面验证 CEIO。

- 端到端性能(图 9-10、表 2):CEIO 将 LLC 缺失率从 88% 降至 1%,吞吐量较 baseline 提升 1.3-2.1×、较 HostCC/ShRing 提升最高 2.9×,P99.9 延迟降低最高 4.73×,动态流量与网络突发场景优势更明显。

- 微观行为(图 11-12、表 3-4):快速路径开销可忽略,慢路径在大消息下性能接近快速路径;数千流场景下活跃流策略仍保持高吞吐;混合流中信用重分配 + 异步机制进一步提升 CPU-involved 流性能。

- 局限场景:小内存压力或超大包时 LLC 不再是瓶颈,CEIO 收益有限。 作者还提炼了三条重要经验:零拷贝对释放 CEIO 潜力至关重要、慢路径在小包多流时仍有优化空间、CEIO 与传输层 CCA 互补共存。

8. 相关工作与结论 第 7 节将 CEIO 与软件级(PacketMill、Shenango)、硬件级(LLC 扩容、DDIO 重分配)以及新型 I/O 加速器(Enso、SRNIC)对比,强调 CEIO 的正交性和可组合性。第 8 节结论重申:CEIO 通过 NIC 入口的主动控制与弹性缓冲,彻底解决了 LLC 低效问题,在商品 SmartNIC 上实现近线速、微秒级 I/O,为未来网络库和 NIC 硬件设计提供了重要指导。致谢部分感谢审稿人与 shepherd,并列出资助来源。