1. 摘要(Abstract)

本文研究的是大模型推理中的通信瓶颈问题,具体聚焦在 Tensor Parallelism(TP)推理场景下的 All-Reduce 加速。随着 LLM 参数规模不断扩大,单个 GPU 很难独立完成低延迟推理,多加速器并行已经成为常态。但在 TP 推理中,每一层 attention 和 MLP block 后通常都需要 All-Reduce,同步各个加速器上的中间结果。这些通信操作直接位于推理关键路径上,无法像训练反向传播那样较好地与计算重叠,因此会明显拖慢端到端推理速度。

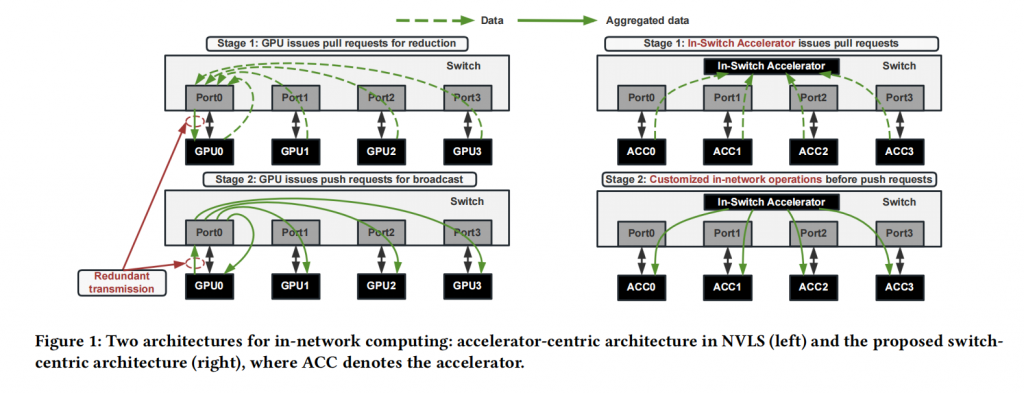

现有方案中,NVIDIA NVLink SHARP(NVLS)已经把部分 reduction 操作下沉到交换机中执行,但它仍然属于 accelerator-centric 架构:由 GPU 发起 load 指令触发交换机内 reduction,结果还要先返回发起 GPU,再由 GPU 推送回交换机进行广播。这会造成额外数据往返。同时,NVLS 依赖 memory-semantic instructions,难以支持更灵活的网络内操作,例如本文提出的 in-network quantization(INQ)。

针对这些问题,论文提出 SCIN(Switch-Centric In-Network Architecture),即一种面向多加速器共享内存网络的交换机中心式网络内计算架构。SCIN 的核心是把一个 In-Switch Accelerator(ISA) 放到交换机中,由 ISA 主动访问各加速器内存、执行 All-Reduce,并把结果直接写回参与设备。这样可以减少冗余数据移动和同步开销。同时,ISA 内部还加入量化模块,使 All-Reduce 可降到 8-bit 精度,接近实现 2 倍通信压缩,且几乎不损失模型精度。

实验方面,作者实现了一个多 FPGA 原型系统,并用该原型校准网络模拟器。在 8-GPU 系统模拟中,SCIN 相比软件 ring All-Reduce,小消息最高加速 8.7×,大消息最高加速 3.8×;在 LLaMA-2 模型上,最高带来 1.74× TTFT 加速和 1.34× TPOT 加速。整体来看,这篇论文不是单纯优化一个通信算法,而是从系统架构层面重新思考:大模型推理中的 collective communication 是否应该由 GPU 主导,还是应该真正交给交换机来主导。

2. 研究背景与问题动机(Introduction)

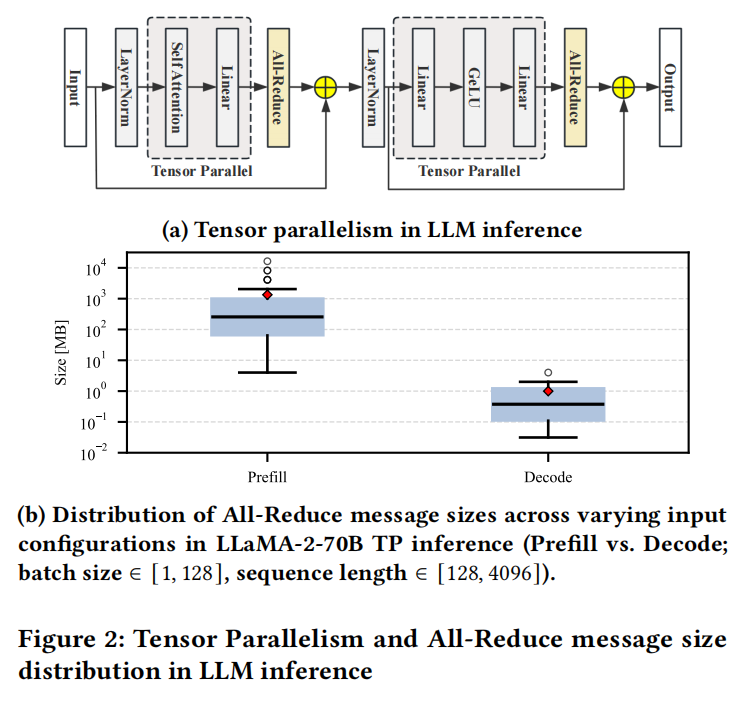

LLM 推理对多加速器系统的依赖越来越强。一方面,大模型参数量和 KV cache 占用不断增长,单卡显存很难承载;另一方面,线上推理又要求较低延迟,因此需要通过 tensor parallelism 把矩阵计算切分到多个加速器上执行。TP 的好处是降低单个加速器的计算和存储压力,但代价是每层都会引入大量 All-Reduce 通信。论文指出,在 TP 推理中,每个 transformer layer 通常会在 attention 和 MLP 后各进行一次 All-Reduce。

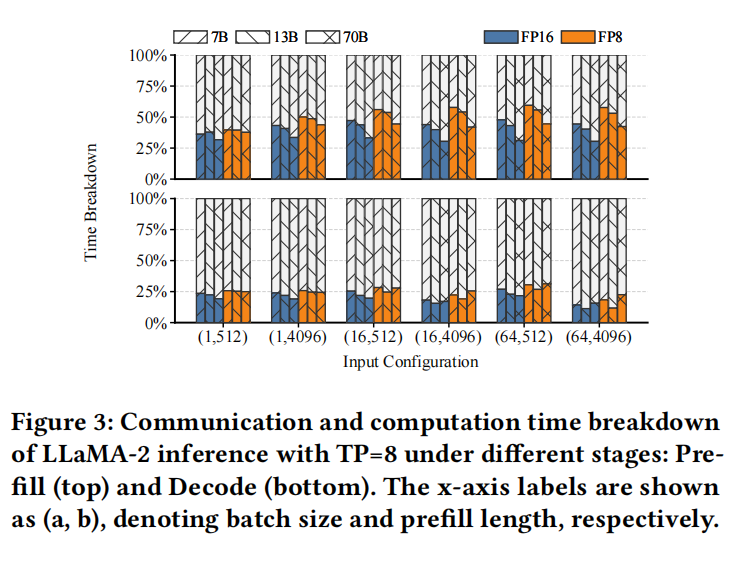

这个问题在推理阶段尤其严重。训练中的梯度 All-Reduce 有时可以和反向传播计算重叠,但推理中的 All-Reduce 位于前向计算关键路径上,GPU 必须等通信完成后才能继续执行下一层。因此,通信延迟会直接转化为用户感知的推理延迟。论文中还区分了两个推理阶段:prefill 阶段 All-Reduce 消息大,更偏带宽瓶颈;decode 阶段 All-Reduce 消息小但次数多,更偏延迟瓶颈。也就是说,好的互连系统必须同时满足高带宽和低延迟。

现有 NVLS 通过在 NVSwitch 中执行 reduction,已经比纯软件 ring All-Reduce 更进一步。但它的问题在于,架构仍然围绕 GPU 展开。GPU 先发起 pull request,交换机完成 reduction 后,结果必须返回 GPU,再由 GPU 发起 push request 做广播。这种路径天然多了一次无用数据传输。此外,由于 NVLS 通过 GPU memory instruction 触发网络内操作,它能支持的操作类型有限,无法很好地支持 INQ 这类更复杂的网络内处理。

本文的动机正是:如果 All-Reduce 的主要瓶颈已经发生在网络中,那么是否应该让交换机真正成为执行主体?SCIN 的回答是肯定的。它把架构从 GPU 主导转向交换机主导,让 ISA 主动读写加速器内存,完成 reduction、quantization 和结果写回。这个设计本质上是在把交换机从“转发设备”升级成“推理通信路径上的主动计算节点”。

3. 系统架构与整体设计(System Overview)

SCIN 的核心设计是 switch-centric in-network computing。与 NVLS 不同,SCIN 不再让 GPU 发起和调度整个 All-Reduce,而是在交换机中加入 In-Switch Accelerator(ISA)。ISA 可以通过共享内存网络直接访问连接在交换机上的加速器内存,主动发起 read request,收集数据后在交换机内部完成 reduction,再直接把结果写回到各参与加速器。

这个设计带来几个直接好处。第一,减少冗余传输。NVLS 中 reduction 结果要先回到发起 GPU,再广播给其他 GPU;SCIN 则可以在交换机内完成 reduction 后直接广播或写回,减少数据绕路。第二,降低同步开销。由于 ISA 位于交换机中心,端点加速器只需和交换机同步,不需要经过额外的 GPU 间协调路径。第三,释放加速器资源。SCIN 把 collective operation 尽可能下沉到 ISA,GPU 只负责轻量同步,更多资源可以留给模型计算。

SCIN 的另一点重要设计是可定制 ISA data plane。作者不仅用它做普通 All-Reduce,还在 ISA pipeline 中加入 quantization/dequantization 模块,实现 INQ All-Reduce。这使得 All-Reduce 可以在网络内被压缩到 8-bit,减少通信量。相比 ring-based quantization 需要随着 TP size 增加进行多轮量化,SCIN 的 INQ 只引入一次额外量化,因此更容易控制误差。

整体来看,SCIN 的架构不是单点优化,而是围绕 TP 推理的两个瓶颈分别处理:decode 阶段通过减少网络跳数和同步延迟解决小消息低延迟问题;prefill 阶段通过 INQ 减少大消息通信量,解决带宽问题。这一点是它比普通通信优化更完整的地方。

4. 关键技术设计(Design and Implementation)

SCIN 的实现主要解决三个问题:协议如何支持 ISA 访问加速器内存、ISA 如何与加速器同步、交换机内部如何高效完成乱序数据处理与 All-Reduce。

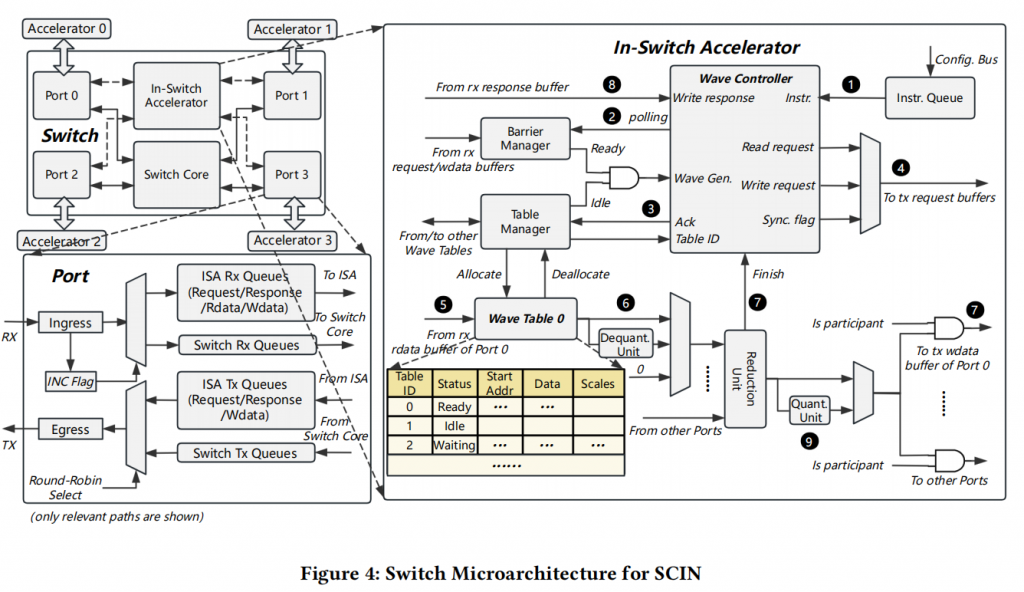

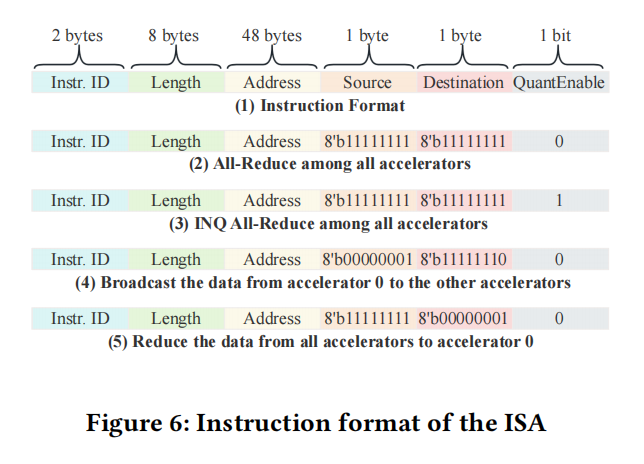

首先是协议扩展。传统交换机协议主要负责 packet forwarding,但 SCIN 要让 ISA 直接参与 memory transaction。为此,作者没有大幅重写协议,而是在 packet header 中加入一个 1-bit INC flag,用来区分普通转发流量和 ISA 相关流量。交换机端口内部将队列拆成两组:一组服务普通 switch forwarding,一组服务 ISA memory transaction。这样既支持 ISA 主动访问加速器内存,又尽量减少对原有网络功能的干扰。

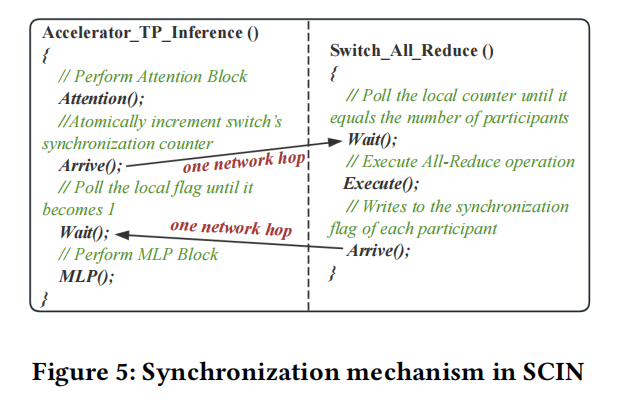

其次是同步机制。TP 推理中的 All-Reduce 位于 attention 和 MLP 之间,任何同步等待都会进入关键路径。SCIN 中,加速器完成前一段计算后,会对 ISA 中的同步计数器做 atomic increment,然后等待本地 flag。ISA 看到所有参与者都到达后,执行 All-Reduce;完成写回后,再通知各加速器继续计算。相比 accelerator-centric 方法需要 GPU 间通过交换网络同步,SCIN 把同步路径缩短到加速器与交换机之间的一跳,因此同步延迟更低。

第三是 ISA 内部的数据流设计。由于多个加速器的 DMA 并发访问会导致数据包乱序返回,ISA 需要提前预留 buffer,并把返回数据放到正确位置。论文提出 wave-based regulation:把大请求拆成多个 wave,每个 wave 占用一部分 buffer,并允许多个 wave 同时在网络中 outstanding。这样可以在有限 buffer 下隐藏同步空隙,提高带宽利用率。ISA 内部通过 wave controller 和 wave table 管理请求发出、数据缓存、reduction、写回和资源释放。

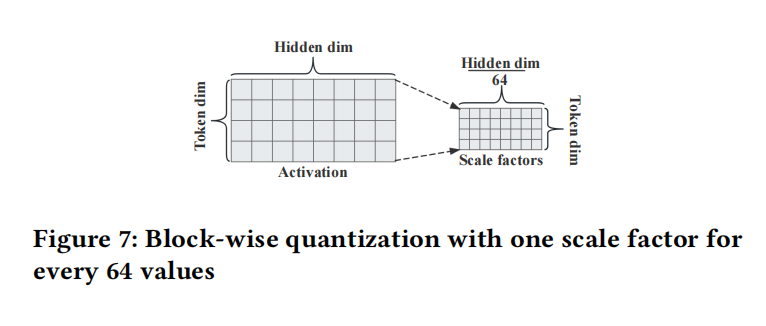

最后是 INQ All-Reduce。作者采用 block-wise quantization,每 64 个 hidden dimension 元素共享一个 scale factor。执行时,ISA 先读取 scale factor 和 activation,再在 pipeline 中完成 dequantization、reduction 和 quantization。这个方案的关键不是“量化”本身,而是量化发生在交换机内,且只发生一次,因此不会像 ring-based 方法那样随着通信轮数累积误差。

5. 原型系统与实验设置(Prototype and Methodology)

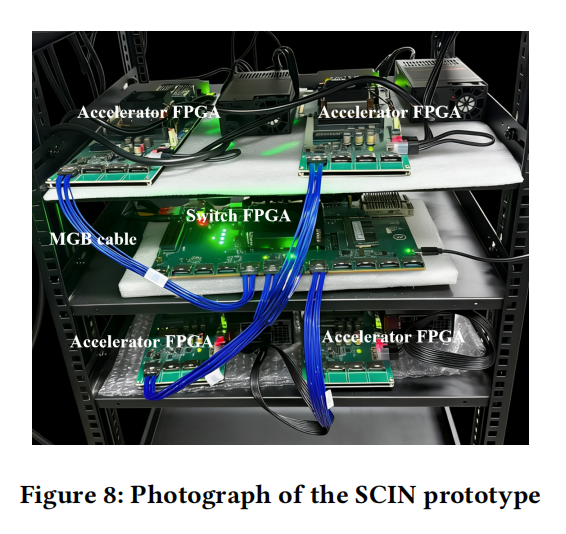

为了证明 SCIN 不是纯概念设计,作者实现了一个多 FPGA 原型系统。该原型包含 4 个 endpoint FPGA,用来模拟加速器,以及 1 个 switch FPGA,用来实现交换机和 ISA。系统使用 AMD Aurora IP 实现物理层和链路层,传输层则按照不同 memory transaction 类型设置独立 buffer,并使用 credit-based flow control。

在原型中,每条链路由 4 条 GT lane 组成,每条 lane 提供 32 Gbps 双向带宽,因此每条 link 的聚合双向带宽为 128 Gbps。系统 flit size 为 32B,运行频率为 250MHz,wave size 设置为 4KB。原型测得 4KB 消息 All-Reduce 延迟为 2.62 μs,16MB 消息延迟为 2.27 ms;大消息下 All-Reduce 带宽利用率达到 92.4%。这说明 SCIN 的数据通路在真实硬件上可以跑起来,并且带宽利用率较高。

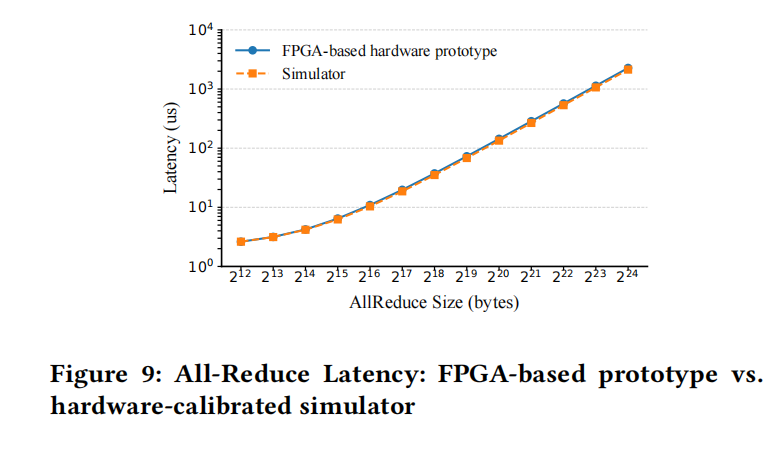

不过,FPGA 原型在带宽和规模上无法直接等价于真实 GPU 集群。因此作者进一步构建了一个 cycle-level network simulator,并用 FPGA 原型结果进行校准。校准后,模拟结果和实测结果误差低于 6%,说明这个模拟器可以用于评估更大规模、更接近实际部署的 8 加速器系统。

计算侧,作者基于 TensorRT-LLM 对 LLaMA-2 模型在 H200 GPU 上进行 profiling,再结合网络模拟器评估 SCIN 对端到端 TP 推理的影响。量化评估则基于 SmoothQuant 代码框架,测试 INQ All-Reduce 对多个模型和多个任务精度的影响。

6. 实验结果与性能分析(Evaluation)

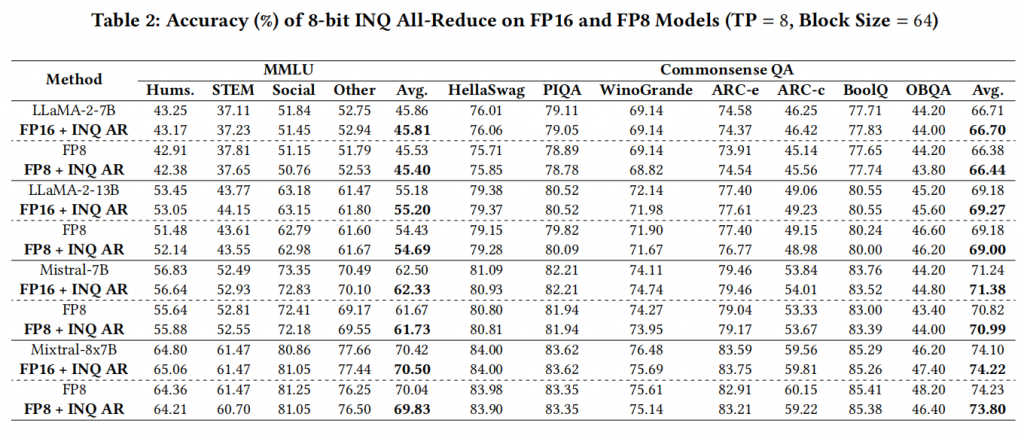

首先是 INQ 的精度影响。作者比较了 INQ All-Reduce 和 ring-based quantized All-Reduce(RQ)。结果显示,在 INT8、block size=64 的设置下,INQ 基本保持 FP16 baseline 的 perplexity,仅有极小退化;在 INT4 更激进的设置下,INQ 也明显优于 RQ。这说明 SCIN 的网络内量化确实比 ring-based 多轮量化更稳定,因为它避免了量化误差随 TP 通信轮数反复累积。

进一步的多模型精度实验也支持这一点。作者在 LLaMA-2-7B、LLaMA-2-13B、Mistral-7B、Mixtral-8x7B 等模型上测试 8-bit INQ All-Reduce,任务包括 MMLU 和多个 commonsense QA benchmark。总体结果显示,INQ 在 FP16 和 FP8 模型上都只带来极小精度波动,有些任务甚至略有提升。因此,本文最终选择 INT8、block size=64 作为默认方案,用接近无损的方式换取接近 2 倍通信压缩。

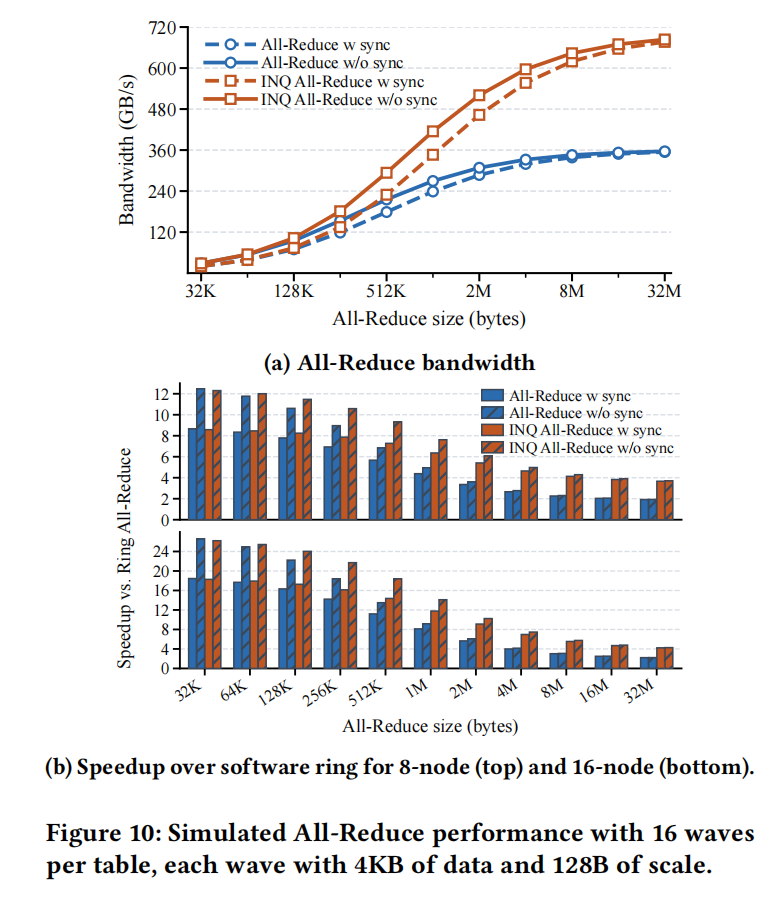

其次是 All-Reduce 带宽和延迟。模拟结果显示,SCIN 在大消息场景下可以接近最大 payload bandwidth;INQ All-Reduce 由于减少通信量,在等效带宽上进一步提高。与软件 ring All-Reduce 相比,SCIN 对小消息和大消息都有明显加速,小消息最高达到 8.7×,大消息最高达到 3.8×。这分别对应 decode 阶段的低延迟需求和 prefill 阶段的高带宽需求。

作者还专门评估了 wave regulation。没有 wave regulation 时,即使 buffer 能覆盖 round-trip latency,也只能达到大约 2/3 总带宽;加入多 wave 机制后,随着 wave 数增加,带宽明显提升,并且 16 waves 基本足以支撑满带宽。这个实验说明,SCIN 的性能并不只是来自“把计算放到交换机里”,还依赖于 ISA 内部对 buffer、请求和返回数据的细粒度调度。

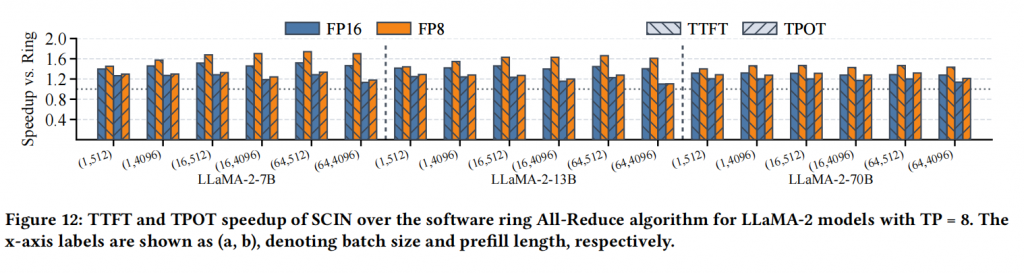

最后是端到端 LLM TP inference。作者在 LLaMA-2 系列模型上评估 SCIN 对 TTFT 和 TPOT 的影响。结果显示,在 FP16 下,SCIN 最高带来 1.52× TTFT 和 1.29× TPOT 加速;在 FP8 下,由于计算更快、通信占比更高,SCIN 的收益更明显,最高达到 1.74× TTFT 和 1.34× TPOT。这也说明一个趋势:未来 GPU 算力继续提升后,通信会越来越成为瓶颈,SCIN 这类网络内计算架构的价值可能会进一步放大。

7. 贡献与结论(Contributions and Conclusion)

本文的主要贡献可以概括为四点:

(1)提出 SCIN,即首个面向多加速器共享内存网络的 switch-centric in-network computing 架构,用交换机中心式设计替代传统 accelerator-centric 设计。

(2)设计 In-Switch Accelerator(ISA) 及其配套通信机制,使交换机能够主动访问加速器内存、执行 All-Reduce,并直接写回结果,从而减少冗余数据传输和同步开销。

(3)提出 In-Network Quantization(INQ),在 ISA 内部完成 All-Reduce 量化,将通信精度降至 8-bit,实现接近 2 倍通信压缩,同时几乎不损失模型精度。

(4)实现多 FPGA 原型,并通过校准模拟器在更大规模系统中评估,最终在 LLaMA-2 TP 推理中取得明显 TTFT 和 TPOT 加速。

这篇论文的研究问题抓得比较准。它没有停留在“通信慢,所以优化通信算法”这一层,而是进一步指出:现有网络内计算架构本身仍然被 GPU 主导,导致数据路径、同步路径和可支持操作都受限制。SCIN 的关键价值就在于把 collective communication 的控制权从 GPU 侧转移到 switch 侧,让交换机真正承担起推理通信路径中的计算和调度功能。

从系统意义上看,这篇工作也反映了一个趋势:未来大模型推理优化不只是模型压缩、kernel 优化或调度策略问题,互连网络本身也会成为 AI 系统设计的一部分。SCIN 的贡献不是单纯让 All-Reduce 更快,而是提供了一个更有扩展性的方向:在 shared-memory accelerator network 中,通过交换机内可编程计算,把通信、量化和同步一起协同优化。